# ECE 272 Lab #6

# Video Graphics Array (VGA)

Marshall Saltz

12/03/2022

#### 1. Introduction

Lab 6 focuses on displaying colors on a monitor using Video Graphics Array (VGA). VGA uses the outputs haync and vaync to draw lines controlled by red, green, and blue. The frame is refreshed when vaync goes to 0, and a new display is drawn. The hardware used for this lab is a monitor, a USB to USB-B cable, a VGA cable, my computer, and a DE10-Lite FPGA. The software used is Quartus Prime Lite 18. The goal of this lab is to use 6 switches to control different levels of red, green, and blue on a monitor.

# 2. Design

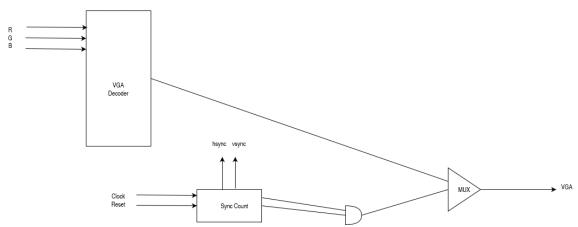

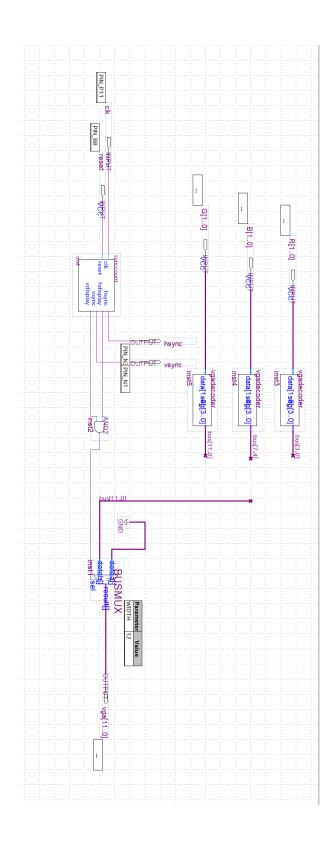

Figure 1: Top Level Block Diagram

The top level block diagram details the logic at the top level. VGA Decoder reads the switches and turns them into VGA signals, which it sends to the multiplexer. Sync count accepts the clock and reset signals and syncs the entire design, outputting hsync, vsync, and to the multiplexer. The multiplexer ultimately chooses which colors to display.

| Interface | Interface      | Input or | Number  | Active         | Board                     | FPGA |

|-----------|----------------|----------|---------|----------------|---------------------------|------|

| Name      | Purpose        | Output   | of Pins | High or<br>Low | Label                     | Pin  |

| clk       | Gate<br>Clock  | Input    | 1       | High           | 50 MHz<br>Clock           | P11  |

| reset     | Gate input     | Input    | 1       | Low            | Push<br>Button            | B8   |

| R[0]      | Gate input     | Input    | 1       | High           | Slide<br>Switch           | C10  |

| R[1]      | Gate input     | Input    | 1       | High           | Slide<br>Switch           | C11  |

| G[0]      | Gate input     | Input    | 1       | High           | Slide<br>Switch           | D12  |

| G[1]      | Gate input     | Input    | 1       | High           | Slide<br>Switch           | C12  |

| B[0]      | Gate input     | Input    | 1       | High           | Slide<br>Switch           | A12  |

| B[1]      | Gate input     | Input    | 1       | High           | Slide<br>Switch           | B12  |

| hsync     | Gate<br>Output | Output   | 1       | Low            | VGA<br>Horizontal<br>Sync | N3   |

| vsync     | Gate<br>Output | Output   | 1       | Low            | VGA<br>Vertical<br>Sync   | N1   |

| vga[0]    | Gate<br>Output | Output   | 1       | High           | VGA<br>Red[0]             | AA1  |

| vga[1]    | Gate<br>Output | Output   | 1       | High           | VGA<br>Red[1]             | V1   |

| vga[2]    | Gate<br>Output | Output   | 1       | High           | VGA<br>Red[2]             | Y2   |

| vga[3]    | Gate<br>Output | Output   | 1       | High           | VGA<br>Red[3]             | Y1   |

| vga[4]    | Gate<br>Output | Output   | 1       | High           | VGA<br>Green[0]           | W1   |

| vga[5]    | Gate<br>Output | Output   | 1       | High           | VGA<br>Green[1]           | T2   |

| vga[6]    | Gate<br>Output | Output   | 1       | High           | VGA<br>Green[2]           | R2   |

| vga[7]    | Gate<br>Output | Output   | 1       | High           | VGA<br>Green[3]           | R1   |

| vga[8]  | Gate   | Output | 1 | High | VGA     | P1 |

|---------|--------|--------|---|------|---------|----|

|         | Output |        |   |      | Blue[0] |    |

| vga[9]  | Gate   | Output | 1 | High | VGA     | T1 |

|         | Output |        |   |      | Blue[1] |    |

| vga[10] | Gate   | Output | 1 | High | VGA     | P4 |

|         | Output |        |   |      | Blue[2] |    |

| vga[11] | Gate   | Output | 1 | High | VGA     | N2 |

|         | Output | _      |   |      | Blue[3] |    |

Figure 2: Interface Definition

The interface definition defines pins for each input and output.

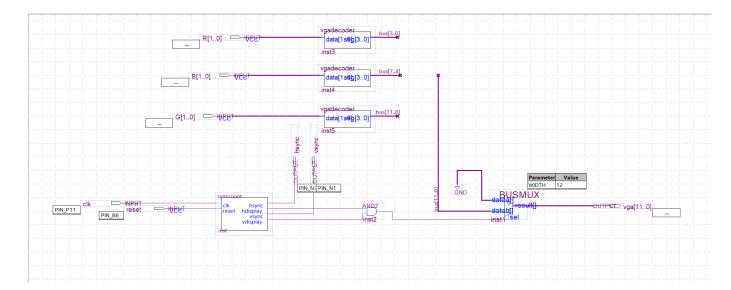

Figure 3: Sync Count Schematic

Sync Count takes in clock and reset and uses a series of comparators, counters, or gates, and an and gate to determine the vertical sync, horizontal sync, and vertical and horizontal displays.

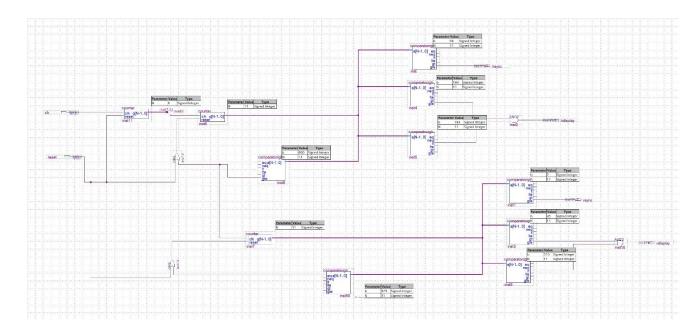

Figure 4: Top Level Schematic This is the block diagram put into action, and follows the same logic.

#### 3. Results

The monitor was able to display varying levels of red, green, and blue depending on which switches on the FPGA were pushed. I do not have photos of this, as I forgot to take them when I had access to a monitor and VGA cable. The code and schematics worked as intended.

# 4. Experiment Notes

Another long lab; who would have thought that displaying visuals from bits and bytes could be so difficult. Ultimately what gave me the most trouble was figuring out in which order to place the comparators in sync count. Most of the lab relied heavily on the previous labs, which made it easier.

### 5. Study Questions

- 1. 307200 pixels are displayed. I got this number by multiplying the width of the display by the height, so 640 pixels times 480 pixels.

- 2. The video driver is 25 MHz, which is from the divided input of the 50 MHz clock input.

- 3. There are 6 switches used, so the display would be able to show 720 colors. This is found by calculating 6 factorial.

# 6. Appendix

```

module countersix#(parameter N=8)(input logic clk, input logic

reset, output logic [N-1:0] q);

always_ff @(posedge clk, posedge reset)

if(reset) q <=0;

else q <= q+1;

endmodule</pre>

```

Figure 5: Counter

This is the counter SystemVerilog code.

```

module comparatorrgb #(parameter b = 96, N = 10)(input logic [N-

1:0] a, output logic eq, neq, lt, lte, gt, gte);

assign eq = (a == b);

assign neq = (a != b);

assign lt = (a < b);

assign lte = (a <= b);

assign gt = (a > b);

assign gt = (a > b);

endmodule

```

Figure 6: Comparator

This is the comparator SystemVerilog code.

Figure 7: Decoder This is the decoder SystemVerilog code.

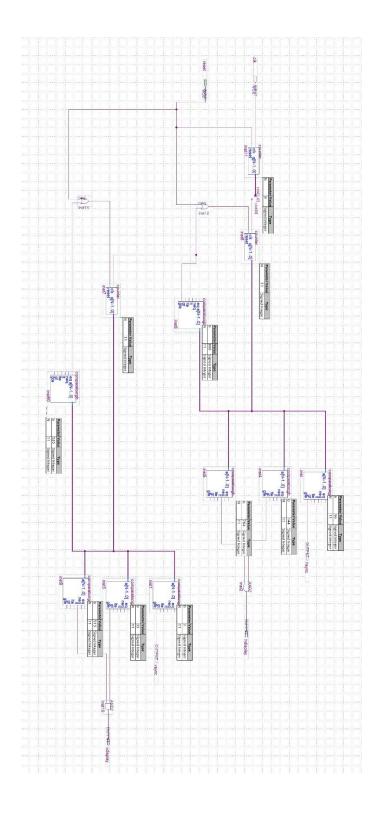

Figure 8: Sync Count Blown Up This is Figure 3 blown up.

Figure 9: Top Level Blown Up This is Figure 4 blown up.